# Design and Performance of Low-Current GaAs MMIC's for L-Band Front-End Applications

Yuhki Imai, Masami Tokumitsu, and Akira Minakawa

**Abstract**—GaAs MMIC's with very low current and of very small size have been developed for L-band front-end applications. The MMIC's fully employ lumped LC elements with uniplanar configurations. There are two kinds of MMIC's: a low-noise amplifier and a mixer. The low-noise amplifier has a noise figure of 2.5 dB and a gain of 11.5 dB. The mixer has a conversion gain of 12.5 dB with small LO power of  $-3$  dBm. Total current dissipation of the two MMIC's is less than 8 mA with 3 V drain bias voltages.

## I. INTRODUCTION

THE recent development of GaAs monolithic microwave integrated circuits (MMIC's) promises highly integrated, low-cost modules for system applications [1]. So far, however, power consumption of MMIC's has not been of great concern in designs, although it is very important in battery-operated instruments such as portable radio units. In portable radio communications, the need for GaAs MMIC's is obvious because MMIC's allow a substantial reduction in size and weight of the unit. For this application, MMIC's have to be designed to operate at very low current levels to conserve the battery drain in portable units [2], [3].

This paper reports the development of GaAs MMIC's with very low dissipation for L-band front-end applications. There are two kinds of MMIC's: a low-noise amplifier and a mixer. A key feature of the MMIC design is the use of lumped *LC* matching circuits with a uniplanar configuration to realize low current dissipation and small size. Here, we present the design, fabrication, and test results for the MMIC's developed.

## II. CIRCUIT DESIGN

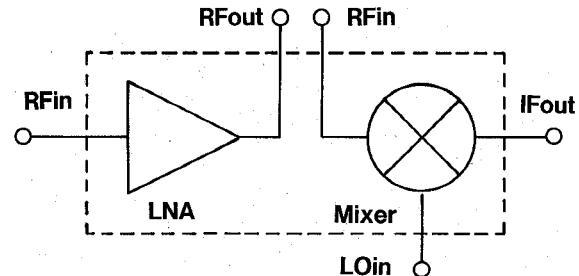

Fig. 1 shows the front-end module design, consisting of a low-noise amplifier and an FET mixer. The module was designed to use an external filter to reject out-of-band noise. Circuits were designed using the circuit simulator SPICE with a modified FET model and Touchstone.

### A. Low-Noise Amplifier

The key issue in minimizing current dissipation is achieving a low noise figure and a high gain using FET's with the

Fig. 1. Block diagram of L-band front-end module.

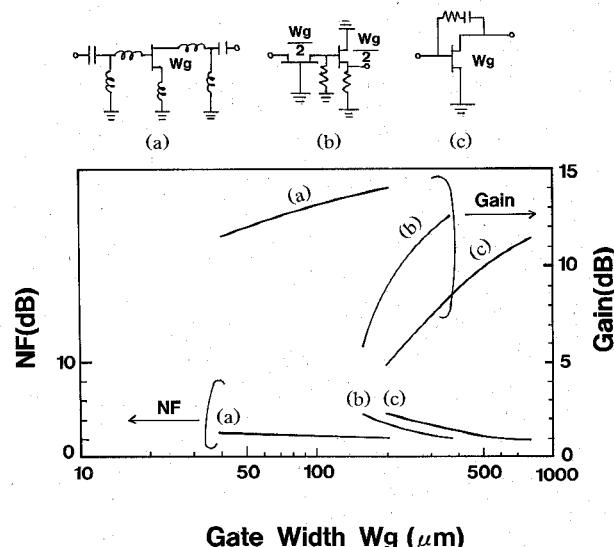

Fig. 2. Simulated gate-width dependencies of RF performance for low-noise amplifiers: (a) Lumped *LC* matching amplifier; (b) active matching amplifier; (c) *RC* feedback amplifier.

narrowest possible gate width. It was from this point of view that we approached our study of an optimum amplifier circuit. Fig. 2 shows three kinds of amplifier circuits and their simulated gate-width dependencies on RF performance. Circuit A fully employs lumped *LC* elements for impedance matching. Circuit B is an active matching amplifier that cascades common-gate and source-follower FET's [4]. Circuit C uses an *RC* feedback configuration for impedance matching [5]. Circuits B and C were generally adopted for UHF and L-band amplifier IC's for the broad bandwidths they allow. The performance of each circuit was

Manuscript received May 15, 1990; revised September 17, 1990.

Y. Imai is with the NTT LSI Laboratories, 3-1, Morinosato Wakamiya, Atsugi-shi, Kanagawa 243-01, Japan.

M. Tokumitsu and A. Minakawa are with the NTT Radio Communications Systems Laboratories, 1-2356 Take, Yokosuka-shi, Kanagawa 238-03, Japan.

IEEE Log Number 9041093.

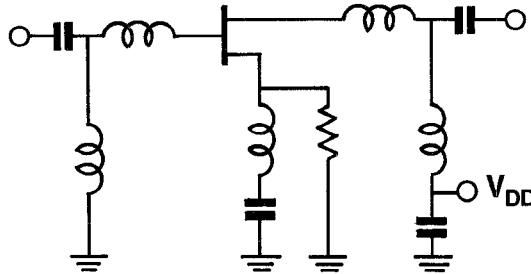

Fig. 3. Circuit schematic of low-noise amplifier.

simulated using an FET with 200 mS/mm transconductance and 50 mA/mm drain current. The noise figure and the gain were simulated at a frequency of 1.6 GHz with the matching condition that input and output reflection coefficients  $S_{11}$  and  $S_{22}$  were better than  $-10$  dB. An active matching amplifier (circuit B) required a total gate width of greater than  $350\ \mu\text{m}$  to obtain better than 3 dB noise figure and 10 dB gain. For this circuit, a gate width of less than  $150\ \mu\text{m}$  was difficult to use because it severely degraded the matching characteristics. An  $RC$  feedback amplifier (circuit C) also required a large gate width of  $500\ \mu\text{m}$  to achieve the same performance because it needs a high transconductance to improve the noise figure and gain. On the other hand, a lumped  $LC$  matching amplifier (circuit A) was expected to have less than one fifth the gate width of these amplifiers to obtain a low noise figure and a high gain. Therefore, the lumped  $LC$  matching configuration allowed very low current operation of a low-noise amplifier using the narrow-gate-width FET.

Fig. 3 shows a schematic circuit of the low-noise amplifier. The amplifier used a  $100\text{-}\mu\text{m}$ -gate-width FET with self-bias circuitry. Inductive series feedback at the source was employed to improve amplifier input VSWR and stability. Applying self-bias circuitry, the gate bias was optimized for low-current operation as well as high RF performance.

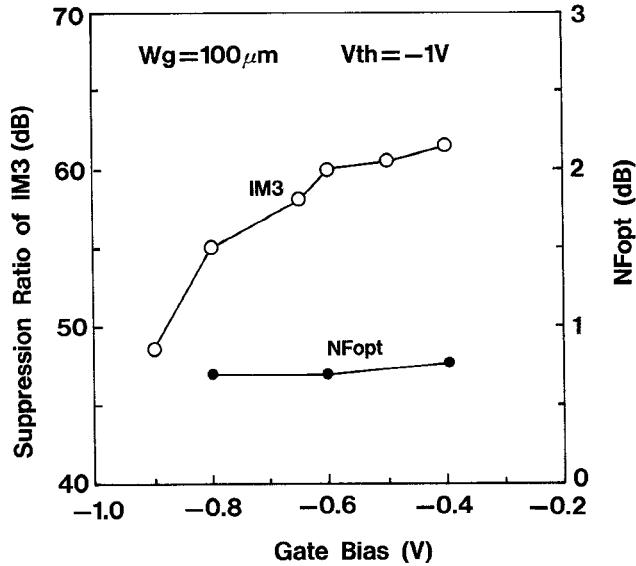

Fig. 4 shows the measured gate-bias dependencies of the FET optimum noise figure,  $NF_{\text{opt}}$ , and the suppression ratio of a third-order intermodulation product, IM3. IM3 was measured using two-tone equal-level input signals with  $-30$  dBm power and 1.6/1.605 GHz frequencies. The gate width and threshold voltage of the FET were  $100\ \mu\text{m}$  and  $-1\text{ V}$ . Based on the results, a gate bias of  $-0.6\text{ V}$  was selected to provide a low-current operation with low  $NF_{\text{opt}}$  and IM3.

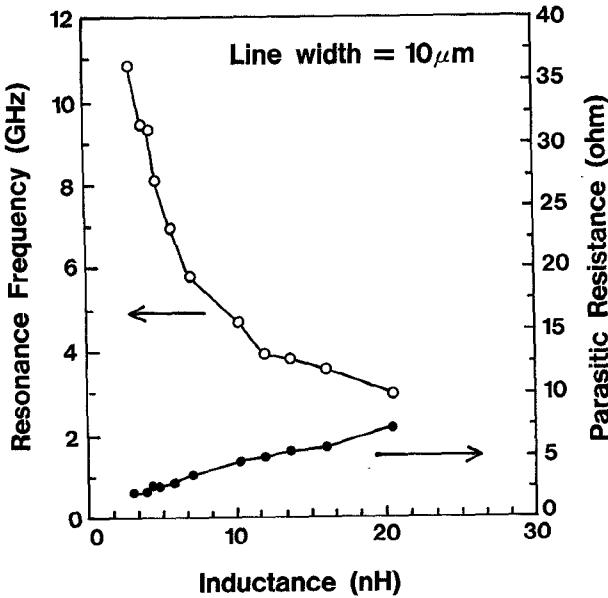

To use lumped  $LC$  matching elements in an L-band MMIC, a monolithic spiral inductor with a large inductance is necessary. Since a spiral inductor needs a high turn with a long line length to increase the inductance value, the parasitic elements are large and adversely affect the MMIC performance. Fig. 5 shows measured parasitic resistance and resonance frequency versus an inductance for monolithic spiral inductors. The line width and space of the spiral inductor were  $5\ \mu\text{m}$  to  $10\ \mu\text{m}$  to reduce the size. For an accurate MMIC design within 1–2 GHz frequency band, a spiral inductor with a resonance frequency greater than 4 GHz was used. On this condition, the spiral inductors employed in the MMIC's were held below  $12\ \text{nH}$ . The parasitic resistance also has a large influence on the MMIC performance, especially the amplifier noise figure owing to the loss of the input matching circuit. Therefore, the spiral inductor used three-level metal interconnect layers and a via

Fig. 4. Gate-bias dependencies of  $NF_{\text{opt}}$  and a suppression ratio of IM3.

metal to reduce the parasitic resistance. The total thickness was about  $4\ \mu\text{m}$ . The resistance was less than  $5\ \Omega$  for the spiral inductor used.

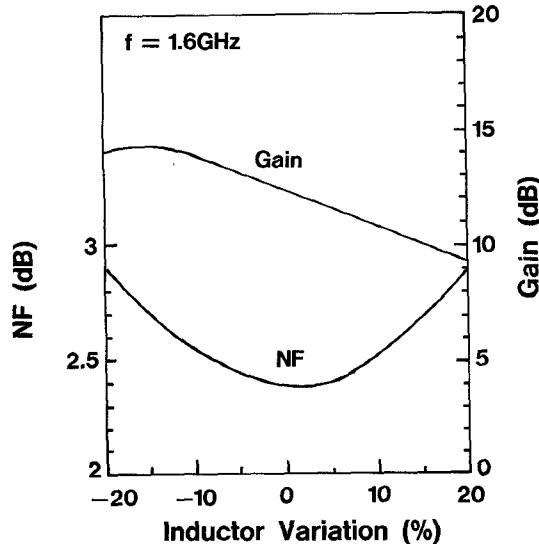

RF performance of a lumped  $LC$  amplifier is mainly affected by the variations of the matching circuit elements. Fig. 6 shows the sensitivity of the circuit to variations of the inductor value. In the simulation, the values of all spiral inductors were changed uniformly. The variations of  $NF$  and gain were within 0.2 dB and 3 dB for each 10% increase and decrease of the inductor value. The predicted noise figure and gain for center values were 2.4 dB and 13 dB.

### B. Mixer

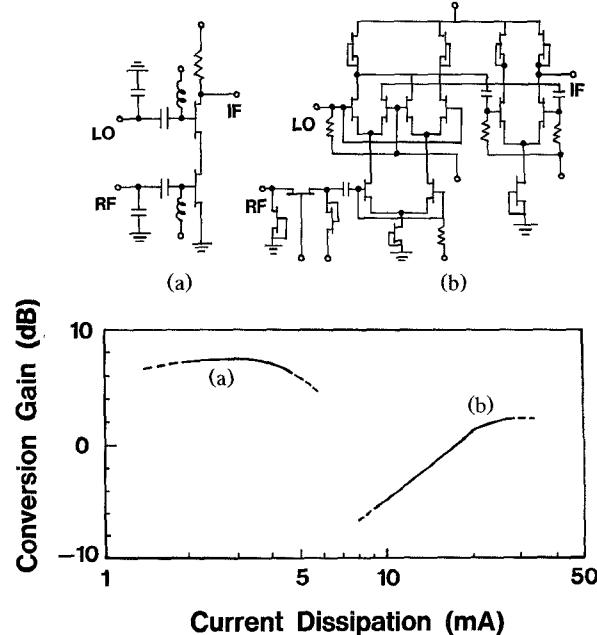

A high conversion gain with a low current dissipation is required for a mixer. Built-in LO/RF isolation is also desirable to eliminate filter circuits. For this purpose, two kinds of mixers were studied, as shown in Fig. 7. Circuit A is a series-connected FET mixer with lumped  $LC$  matching circuits for RF and LO ports [6]. Circuit B is an analog multiplier based on Gilbert's cell [7] with RF and IF buffer amplifiers. Both circuits have good built-in LO/RF isolations. Fig. 7 shows the simulated current dissipation dependencies of the conversion gains for these mixers. The performance was simulated using an FET of 200 mS/mm transconductance and 50 mA/mm drain current. RF and IF frequencies were 1.6 GHz and 50 MHz with an LO power of  $-3$  dBm. Circuit B required a current dissipation of greater than 17 mA to obtain a conversion gain. This is because large-gate-width FET's were required to increase the conversion gain. Circuit A, on the other hand, had a high conversion gain with a current dissipation of less than 5 mA. Therefore, circuit A is well suited to low-current operation with a high conversion gain.

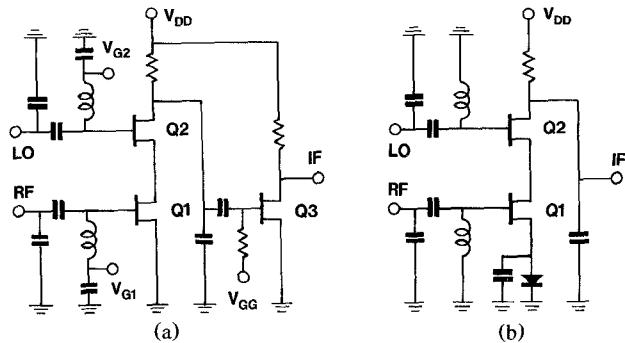

Fig. 8 shows a schematic circuit of a mixer. RF and LO matching were provided using pi-type matching circuits to reduce the number of spiral inductors. A buffer amplifier was used to obtain high gain with small LO power and IF impedance matching. The gate widths of the FET's were  $100\ \mu\text{m}$  and  $80\ \mu\text{m}$  for the mixer and buffer amplifier, respec-

Fig. 5. Resonance frequency and parasitic resistance for monolithic spiral inductors.

Fig. 6. Performance sensitivity to inductor values for a low-noise amplifier.

tively. A mixer with self-bias circuitry was also tested to simplify the power supply requirement. A schematic circuit is shown in Fig. 8. Because of low IF frequency, self-bias circuitry using a resistor with a bypass capacitor at an FET source degraded the conversion gain. Therefore, a level-shifting diode was used instead of a biasing resistor for the self-bias mixer. The mixer used a 200- $\mu$ m-gate-width FET without a buffer amplifier. The predicted conversion gains for the mixers were 13 dB with a buffer amplifier and 5 dB without a buffer amplifier, respectively.

### III. MMIC FABRICATION

MMIC's were fabricated using advanced self-aligned implantation for n<sup>+</sup> layer technology (ASAINT) [8]. The gate length and the threshold voltage were 0.3  $\mu$ m and -1 V. A

Fig. 7. Simulated current dissipation dependencies of conversion gain for mixers: (a) Series-connected FET mixer; (b) Analog multiplier based on Gilbert's cell.

Fig. 8. Circuit schematics of mixers: (a) mixer without self-bias circuitry; (b) mixer with self-bias circuitry.

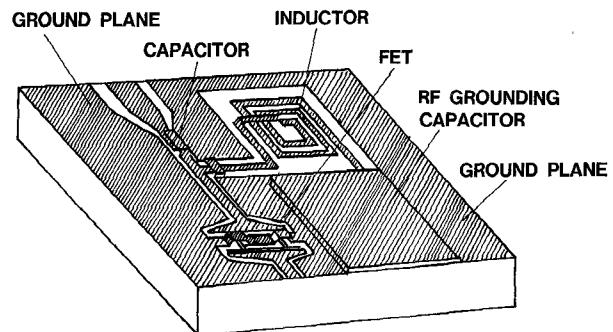

Fig. 9. Uniplanar MMIC configuration with lumped LC elements.

uniplanar configuration was employed for the MMIC's [9]. A schematic of a uniplanar configuration with lumped LC elements is shown in Fig. 9. This configuration has no via holes and includes a coplanar ground plane close to each circuit element for easy access to an RF ground. It permits a compact MMIC layout because the large RF grounding

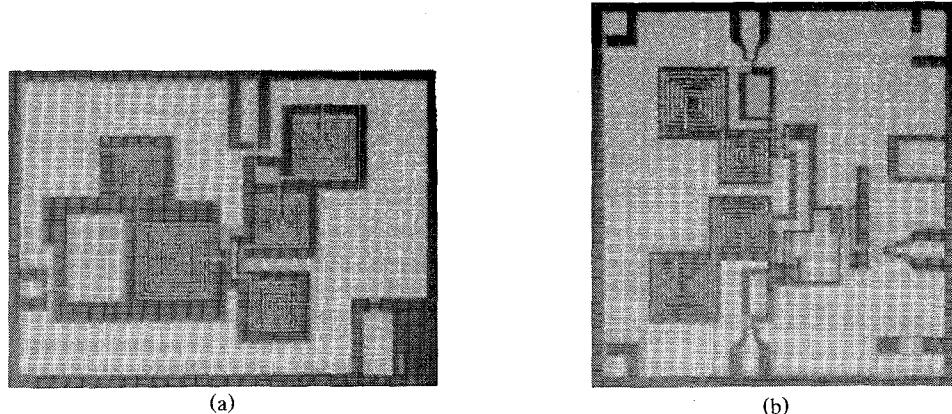

Fig. 10. Microphotographs of MMIC's: (a) low-noise amplifier; (b) mixer.

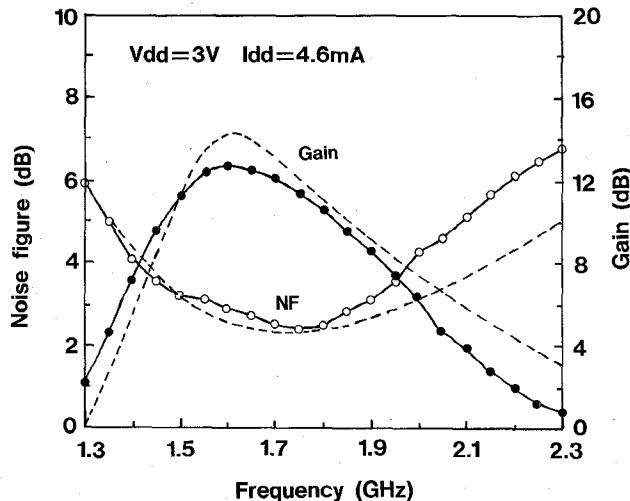

Fig. 11. Frequency dependencies of  $NF$  and gain for a low-noise amplifier. Solid lines: measured results. Dashed lines: simulated results.

capacitors can be easily integrated anywhere on the substrate. This feature is especially effective for L-band applications in which very large RF grounding capacitors are needed. Fig. 10 shows microphotographs of the low-noise amplifier and mixer using a lumped  $LC$  uniplanar configuration. Chip sizes were  $1.5 \times 2 \text{ mm}^2$  for the low-noise amplifier and  $2 \times 2 \text{ mm}^2$  for the mixer. A grounding capacitor with a capacitance exceeding  $10 \text{ pF}$  was used for each biasing line to eliminate an off-chip capacitor.

#### IV. PERFORMANCE

##### A. Low-Noise Amplifier

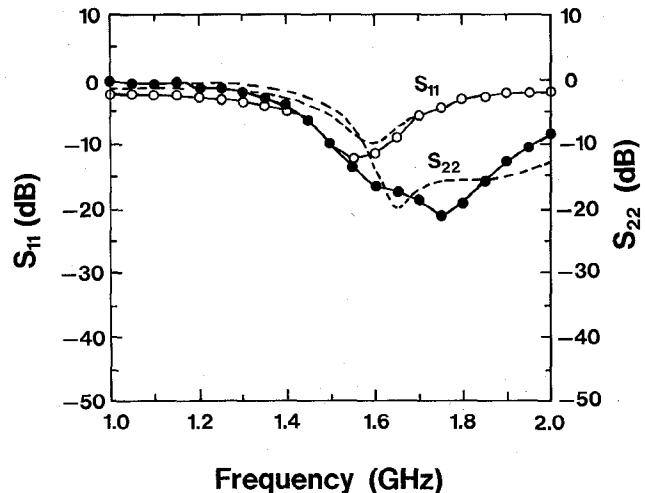

Typical frequency dependencies of the noise figure and gain are shown in Fig. 11. Frequency dependencies of  $S_{11}$  and  $S_{22}$  are also shown in Fig. 12. The amplifier had a current dissipation of  $4.6 \text{ mA}$  and a single bias voltage of  $3 \text{ V}$ . The minimum noise figure was  $2.5 \text{ dB}$  with a gain of  $11.5 \text{ dB}$ . The amplifier had a gain of more than  $11 \text{ dB}$  and a noise figure of less than  $3 \text{ dB}$  in the  $1.5\text{--}1.7 \text{ GHz}$  frequency band. Simulated results are also shown in Figs. 11 and 12; they agree well with the measured results.

Fig. 12. Frequency dependencies of  $S_{11}$  and  $S_{22}$  for a low-noise amplifier. Solid lines: measured results. Dashed lines: simulated results.

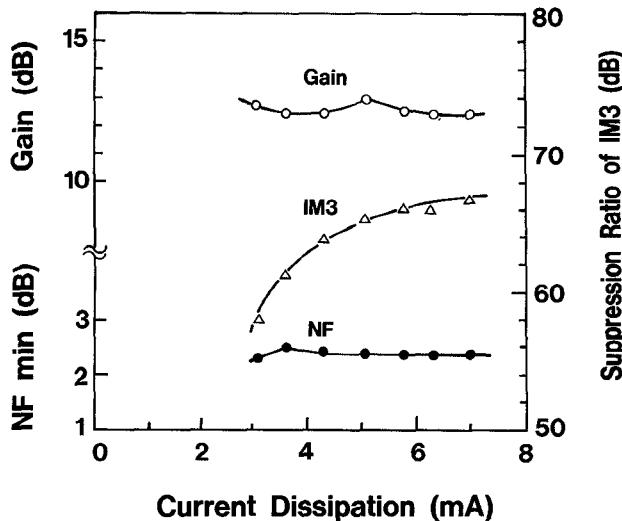

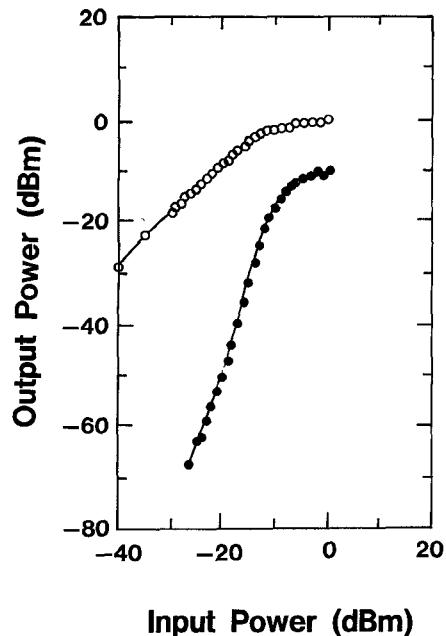

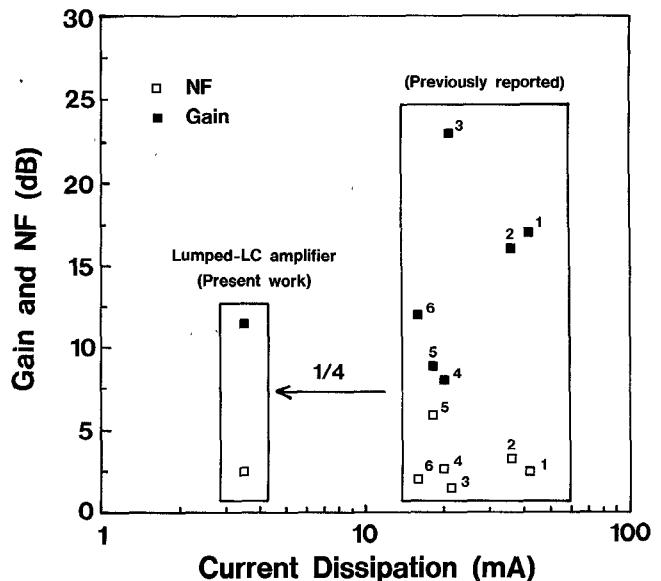

Amplifiers with different threshold voltages, ranging from  $-0.7$  to  $-1.3 \text{ V}$ , were measured to study current dissipation dependences of the RF performance. The results are shown in Fig. 13. The suppression ratio of IM3 was measured at  $-30 \text{ dBm}$  input power with  $1.6/1.605 \text{ GHz}$  input signals. The gain and the noise figure were not degraded with current dissipation down to  $3 \text{ mA}$ . On the other hand, the suppression ratio of IM3 decreased as the current dissipation was reduced. The amplifier with  $3.5 \text{ mA}$  current dissipation provided a suppression ratio of more than  $60 \text{ dB}$ , which is acceptable for most front-end applications. A plot of the output power versus input power for this amplifier is shown in Fig. 14. The intercept point was  $9 \text{ dBm}$ . We compared the current dissipation with previously reported low-noise amplifier MMIC's operating in the L band and UHF bands and the results are shown in Fig. 15. The developed amplifier dissipated only one fourth, the current of previously reported MMIC's in the L and UHF bands [4], [5] [10]–[13].

##### B. Mixer

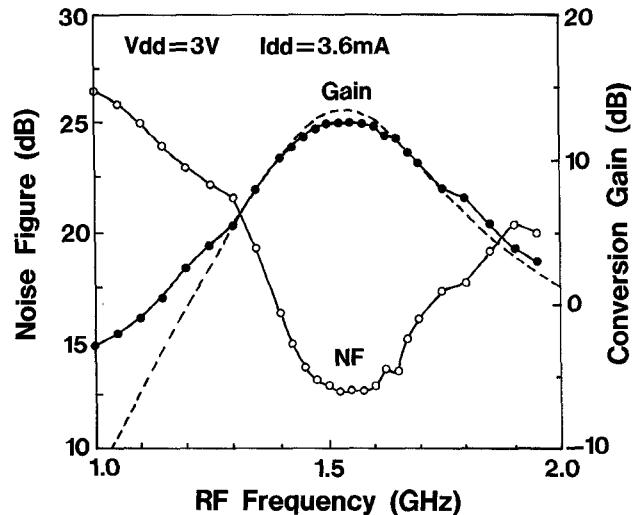

Typical frequency dependencies of the SSB noise figure and conversion gain for the mixer with buffer amplifier are shown in Fig. 16. LO power and IF frequency were  $-3 \text{ dBm}$

Fig. 13.  $NF$ , gain, and suppression ratio of IM3 versus current dissipation for amplifiers with different threshold voltages.

Fig. 14. Output power versus input power for amplifier with 3.6 mA current dissipation:  $\circ$  fundamental frequency;  $\bullet$  third-order intermodulation product.

and 50 MHz. The current dissipation was 3.6 mA with 3 V drain bias and additional gate biases. The mixer had a maximum conversion gain of 12.5 dB with a noise figure of 12.6 dB. The simulated conversion gain using SPICE agreed well with the measured results. The suppression ratio of IM3 was measured under the same condition as the low-noise amplifier. The suppression ratio of IM3 and the gain were 46 dB and 12.5 dB for high-gain gate biases. For the medium-gain gate biases, the values were 63 dB and 8.3 dB. LO/RF isolation and LO/IF isolation were better than 20 dB and 30 dB, respectively.

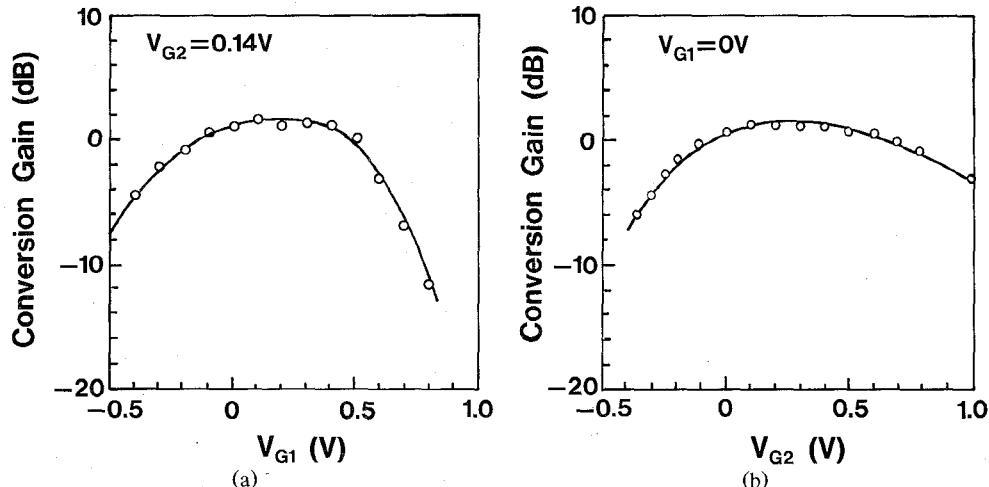

Fig. 17 shows gate-bias dependencies of the conversion gain for a mixer with self-bias circuitry. RF and IF frequencies were 1.55 GHz and 50 MHz. The drain bias was 5 V. A

Fig. 15. Low-noise amplifier MMIC's operating in L bands and UHF bands. 1.  $V_{dd} = 4$  V [13]. 2.  $V_{dd} = 5$  V [12]. 3:  $V_{dd} = 8$  V [5]. 4:  $V_{dd} = 1$  V [11]. 5:  $V_{dd} = 6$  V [4]. 6:  $V_{dd} = 5$  V [10]. Present work:  $V_{dd} = 3$  V.

Fig. 16. Frequency dependencies of SSB noise figure and conversion gain for a mixer without self-bias circuitry. Solid lines: measured results. Dashed line: simulated result.

conversion gain greater than 0 dB was obtained in the gate-bias ranges from 0 to 0.5 V for Q1FET and from -0.1 to 0.7 V for Q2FET, respectively. A self-bias mixer thus operated with only positive biases, which greatly simplifies the power supply. The current dissipation and conversion gain were 2.2 mA and 0 dB with 5 V drain and 0 V gate biases.

## V. CONCLUSION

GaAs MMIC's with very low current and small size were developed for L-band front-end applications. Total current dissipation of the low-noise amplifier and mixer was 7.1 mA with a conversion gain of 25 dB using -3 dBm LO power. With these MMIC's, front-end-module size is reduced to about one fifth that of conventional hybrid circuit technolo-

Fig. 17. Gate-bias dependencies of conversion gain for a mixer with self-bias circuitry.  $V_{G1}$ : gate bias of Q1FET.  $V_{G2}$ : gate bias of Q2FET.

gies. The developed MMIC's will have a great effect on telecommunication system applications, such as mobile radio units, thanks to their low current dissipation and small size and the elimination of circuit adjustments.

#### ACKNOWLEDGMENT

The authors wish to thank Y. Yamao for useful discussions on the system applications. They also thank T. Sugita and M. Aikawa for their advice and encouragement.

#### REFERENCES

- [1] T. Hirota, M. Muraguchi, A. Minakawa, and K. Osafune, "A uni-planar MMIC 26-GHz-band receiver," in *IEEE GaAs IC Symp. Tech. Dig.*, 1988, pp. 185-188.

- [2] V. Nair, "Low current enhancement mode MMICs for portable communication applications," *IEEE GaAs IC Symp. Tech. Dig.*, 1989, pp. 67-70.

- [3] Y. Imai, M. Tokumitsu, A. Minakawa, T. Sugita, and M. Aikawa, "Very low-current small-size GaAs MMICs for L-band front-end applications," *IEEE GaAs IC Symp. Tech. Dig.*, 1989, pp. 71-74.

- [4] E. Kemppinen, E. Järvinen, and T. Närhi, "Design of an L-band monolithic GaAs receiver front-end with low power consumption," in *Proc. IEEE Int. Symp. Circuits Syst.*, 1988, pp. 2535-2538.

- [5] M. Nishima *et al.*, "A UHF GaAs multi-stage wideband amplifier with dual feedback circuits," in *IEEE GaAs IC Symp. Tech. Dig.*, 1987, pp. 223-226.

- [6] C. Tsironis, R. Meierer, and R. Stahlmann, "Dual-gate MESFET mixers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, pp. 248-255, Mar. 1984.

- [7] B. Gilbert, "A high-performance monolithic multiplier using active feedback," *IEEE J. Solid-State Circuits*, vol. SC-9, pp. 364-373, Dec. 1974.

- [8] T. Enoki, K. Yamasaki, K. Osafune, and K. Ohwada, "0.3- $\mu$ m advanced SAINT FET's having asymmetric N<sup>+</sup>-layers for ultra high frequency GaAs MMIC's," *IEEE Trans. Electron Devices*, vol. 35, pp. 18-24, Jan. 1988.

- [9] M. Muraguchi, T. Hirota, A. Minakawa, K. Ohwada, and T. Sugita, "Uniplanar MMIC's and their applications," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 1896-1901, Dec. 1988.

- [10] V. Pauker, P. Dautriche, A. Giakoumis, and A. Kazeminejad, "Normally-off MESFET analogue circuits," in *Proc. European Microwave Conf.*, 1984, pp. 631-633.

- [11] J. Tajima, Y. Yamao, T. Sugita, and M. Hirayama, "GaAs monolithic low-power amplifiers with RC parallel feedback," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, pp. 542-544, May 1984.

- [12] K. Osafune, N. Kato, T. Sugita, and Y. Yamao, "A low-noise GaAs monolithic broad-band amplifier using a drain current saving technique," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-33, pp. 543-545, June 1985.

- [13] K. Honjo, T. Sugiura, T. Tsuji, and T. Ozawa, "Low-noise, low power dissipation GaAs monolithic broad-band amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-31, pp. 412-417, May 1983.

**Yuhki Imai** was born in Tokyo, Japan, on March 15, 1955. He received the B.E. and M.E. degrees in applied physics from Waseda University, Japan, in 1977 and 1979, respectively.

He joined the NTT Electrical Communication Laboratories, Musashino, Japan, in 1979.

His work there dealt with the development of InP and GaAs MESFET's and GaAs MMIC's. In 1989 he joined the NTT LSI Laboratories, where he is currently engaged of GaAs IC's for lightwave communication systems.

Mr. Imai is a member of the Institute of Electronics, Information and Communication Engineers of Japan.

**Masami Tokumitsu** received the B.S. and M.S. degrees in electrical communications engineering from the University of Electrical Communications, Tokyo, Japan, in 1979 and 1981, respectively.

From 1981 to 1983, he was with the Musashino Electrical Communication Laboratory, Nippon Telegraph and Telephone Public Corporation. In 1983, he joined the NTT Atsugi Electrical Communication Laboratory. He has been engaged in the design of Josephson integrated circuits and the development of GaAs MESFET's. In 1989, he moved to the NTT Radio Communication Systems Laboratories, where he is presently engaged in research on microwave integrated circuits.

Mr. Tokumitsu is a member of the Institute of Electronics, Information and Communication Engineers of Japan and the Japan Society of Applied Physics.

✉

**Akira Minakawa** was born in Ibaraki, Japan, on May 20, 1960. He received the B.S. and M.S. degrees in electrical engineering

from Ibaraki University, Ibaraki, in 1984 and 1986, respectively.

He joined the Electrical Communications Laboratories of the Nippon Telegraph and Telephone Corporation in 1986. He has been engaged in research on microwave integrated circuits.

Mr. Minakawa is a member of the Institute of Electronics, Information and Communication Engineers of Japan.